The PLONK IOP for general circuits

PLONK: a poly-IOP for a general circuit

Step 1: compile circuit to a computation trace (gate fan-in=2)

The computation trace (arithmetization):

| left inputs: | right inputs: | w | |

|---|---|---|---|

| inputs: | 5 | 6 | 1 |

| Gate 0: | 5 | 6 | 11 |

| Gate 1: | 6 | 1 | 7 |

| Gate 2: | 11 | 7 | 77 |

Encoding the trace as a polynomial

Notion:

,

let (in example, ) and

The plan:

prover interpolates a polynomial that encodes the entire trace.

Prover interpolates such that

(1) encodes all inputs: for

(2) encodes all wires: :

- left input to gate #

- right input to gate #

- output of gate #

In the example, Prover interpolates such that:

| inputs: | |||

|---|---|---|---|

| Gate 0: | |||

| Gate 1: | |||

| Gate 2: |

degree() = 11

Prover can use IFFT to compute coefficients of in time

Step 2: proving validity of

Prover needs to prove that is a correct computation trace:

(1) encodes the correct inputs,

(2) every gate is evaluated correctly,

(3) the wiring is implemented correctly,

(4) the output of last gate is 0

Proving (4) is easy: prove

Proving (1): T encodes the correct inputs

Both prover and verifier interpolate a polynomial that encodes the -inputs to the circuit:

In the example: ( is linear)

constructing takes time proportional to the size of input verifier has time do this.

Let (points encoding the input)

Prover proves (1) by using a ZeroTest on to prove that

Lemma: is zero on if and only if is divisible by

Proving (2): every gate is evaluated correctly

Idea: encode gate types using a polynomial

define such that :

- if gate #l is an addition gate

- if gate #l is a multiplication gate

| inputs: | 5 | 6 | 1 | S(x) |

|---|---|---|---|---|

| Gate 0: | 5 | 6 | 11 | 1(+) |

| Gate 1: | 6 | 1 | 7 | 1(+) |

| Gate 2: | 11 | 7 | 77 | 0(\times) |

Then :

Prover uses ZeroTest to prove that for all :

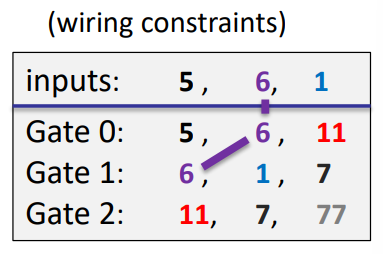

Proving (3): the wiring is correct

encode the wires of :

Define a polynomial that implements a rotation:

Lemma: wire constraints are satisfied

The complete Plonk Poly-IOP (and SNARK)

Prover proves:

gates: (1)

inputs: (2)

wires: (3)

output: (4)